SSD auf einem Chip

Funktionsblöcke monolithisch in einem IC-Gehäuse zusammenfassen

SSD auf einem Chip

Funktionsblöcke monolithisch in einem IC-Gehäuse zusammenfassen

Make or Buy? Beim Einsatz von Flash-Speichern im System spielen viele Faktoren mit, die diese Entscheidung beeinflussen. Wenn der Dreiklang der Performance – Zugriffsgeschwindigkeit, Daten-integrität und Langzeitverhalten – stimmen soll, fällt die Wahl auf eine Disk auf einem Chip. Warum dies langfristig der beste Ansatz ist, erläutert dieser Beitrag.

Autor: Rudolf Sosnowsky, Leiter Technik bei Hy-Line

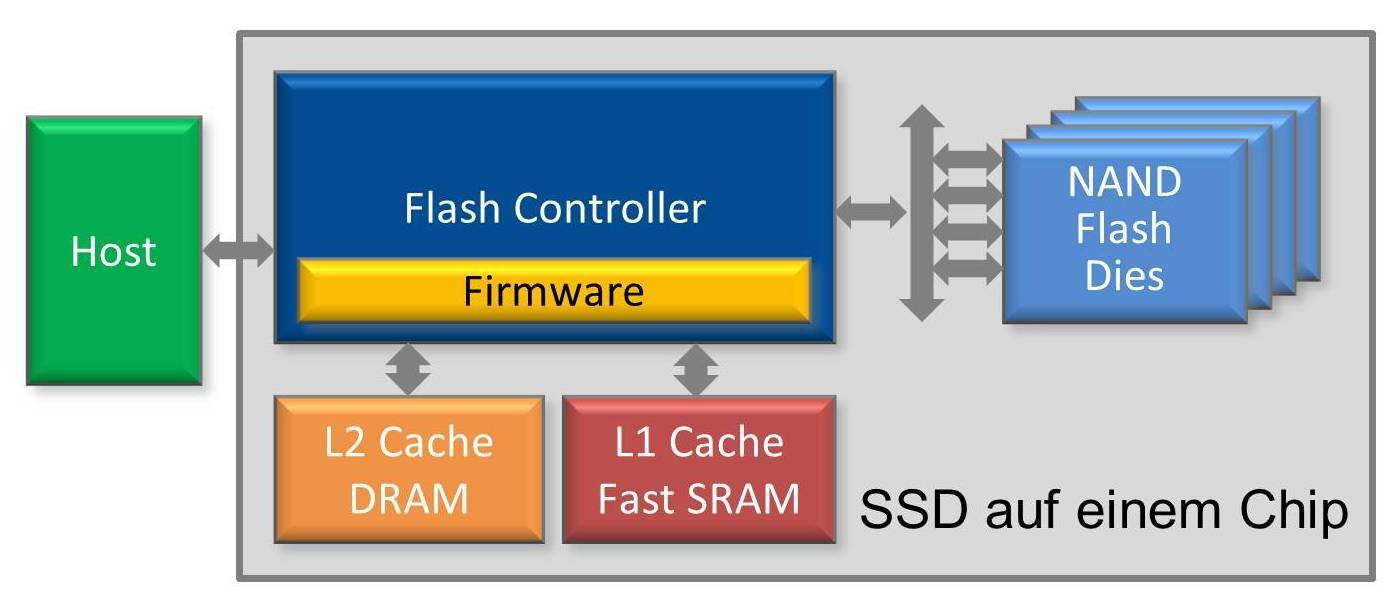

Jeder, der schon einmal einen USB-Stick geöffnet hat, hat die einzelnen Komponenten darin identifiziert: Neben dem oder den Flash-Chips, die die grösste Fläche einnehmen, sitzt der Controller-Chip mit USB- und Flash-Interface sowie die Spannungsversorgung. In höherwertigen Speichermedien wie in einer SSD mit SATA- oder PCIe-Interface kommt oft noch ein RAM hinzu, das den Transfer besonders beim Schreiben von Daten in den Flash-Speicher beschleunigt.

Vorteile einer Single-Chip-Lösung

Für den Einsatz in einer rauen Umgebung ist diese Konfiguration schlecht geeignet. Schock und Vibrationen belasten die Mechanik und die Kontakte, und Temperaturwechsel im industriellen Massstab beanspruchen die Lötstellen. Mit einer Single-Chip-Lösung, die alle Komponenten in einem IC-Gehäuse vereint und hermetisch versiegelt, lassen sich diese Problemstellen vermeiden. Das BGA-Gehäuse kann im üblichen Prozess zusammen mit den anderen Schaltungskomponenten auf der Leiterplatte verlötet werden. Im Folgenden soll der Begriff SSD für alle Speichermedien gelten, bei denen die Flash-Chips über einen Controller unabhängig von der Schnittstelle an ein Host-System angeschlossen werden.

Flash-Technologien

Die Grundlage der Flash-Technologie ist eine zwischen zwei isolierenden Schichten eingeschlossene elektrische Ladung. Beim Beschreiben und Löschen des Speichers werden diese Schichten durch eine erhöhte Spannung kurzzeitig leitfähig, sodass die Ladung sie durchdringen kann. Dies beansprucht die Isolationsschicht; der Isolationswiderstand nimmt im Laufe der Zeit ab, und die Zelle altert. Die Hersteller geben in Datenblättern P/E Cycles an und meinen damit das Programmieren und Löschen (Erase) der Zelle. Eine einzelne Zelle kann nicht gelöscht werden, sondern immer nur ein ganzer Block, so dass das Ändern eines einzigen Bits einen P/E-Zyklus für einen ganzen Block bedeutet.

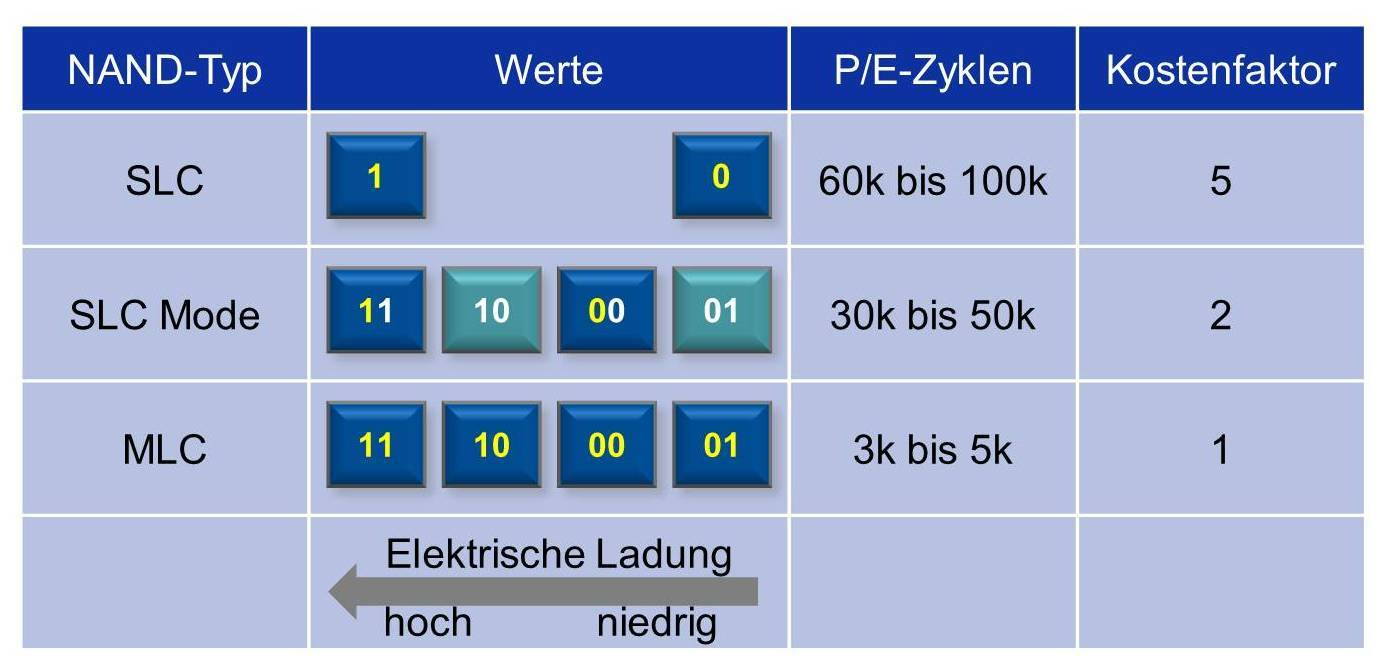

Beim Auslesen wird die Höhe der Ladung ausgewertet, um einen digitalen Wert zu bestimmen. Bei der Single Level Cell (SLC) entscheidet ein Komparator, ob der zurückgelesene Spannungswert kleiner oder grösser als eine definierte Schwelle ist, und gibt dann «0» oder «1» zurück. Bei der (etwas unglücklich benannten) Multi Level Cell (MLC) ist die Abstufung feiner, so dass vier unterschiedliche Spannungspegel als der Zustand zweier Bits (00, 01, 10, 11) interpretiert werden. In fortgeschrittener Halbleitertechnologie wird die Isolation und damit die Ladungshaltung weiter verbessert, so dass Triple Level Cells (TLC) acht verschiedene Spannungswerte halten, die als drei Bits pro Zelle ausgewertet werden. Mit der Quad Level Cell (QLC)-Technologie ist der vorläufige Höhepunkt erreicht.

Mit der höheren Integration durch kleinere Strukturen verringern sich zwar die Kosten pro Bit, Haltbarkeit (Endurance) und die Übertragungsrate (Performance) des Speichers nehmen jedoch ab. Da die NAND-Hersteller der Nachfrage nach höherer Kapazität folgen, sind SLC-Speicher zu moderaten Preisen kaum noch erhältlich. Ein Kompromiss zwischen Kapazität, Zahl der Schreibzyklen und Kosten ist der Betrieb der MLC-Zelle im so genannten «SLC-Mode», der auch als «Pseudo-SLC» bekannt ist. Die MLC-Speicherzelle wird dabei mit nur mit zwei anstatt der möglichen vier Werte beschrieben. Dabei geht nutzbare Kapazität verloren, die aber der Zuverlässigkeit und Langlebigkeit zu Gute kommt. Dieses Verfahren setzt eine enge Zusammenarbeit zwischen Controller- und NAND-Hersteller voraus, da hierbei der interne Aufbau des Flash-Bausteins wichtig ist.

Abb. 2 zeigt, welche Zustände eines MLC-Speichers genutzt werden, um den SLC-Mode abzubilden. Die nicht sequenzielle Abfolge der binären Zustände liegt an der durch die grössere Hamming-Distanz gesteigerten Störfestigkeit. Bei ungefähr doppelten Kosten im Vergleich zum MLC-Betrieb verzehnfacht sich die Anzahl der Schreibzyklen.

Flash-Controller

Flash-Bausteine werden in der Praxis nicht direkt mit einer Host-CPU verbunden. Zwischen den Host und den Speicher ist ein Controller geschaltet, der zur Host-Seite hin ein Standard-Interface anbietet und die Speicher mit Hilfe einer spezialisierten Firmware unter Kontrolle hat. Bei einer SSD leistet der Controller viele Funktionen, um dem Speicher-Subsystem bei höchster Zuverlässigkeit ein langes Leben und hohe Geschwindigkeit zu geben. Dazu gehört das Wear Levelling, mit dem Schreibvorgänge auf den gesamten Speicher verteilt werden, um die Lebensdauer des Systems zu erhöhen, und das Management defekter Blöcke. Eine weitere Funktion ist die Ansteuerung und Verwaltung eines Caches, um die Zugriffsgeschwindigkeit besonders beim Schreiben zu erhöhen. In schnellen Systemen ist dieser Cache mehrstufig (siehe Abb. 3) angelegt.

Die Integration in ein einziges Gehäuse ermöglicht, die Firmware des Controllers auf die Eigenschaften des Speichers zu optimieren. Dabei wird die Performance der Hardware – Zugriffsgeschwindigkeit, Datenhaltung und Endurance – fein abgestimmt. Für eine kostengünstige Lösung wird TLC-Speicher eingesetzt. Teile des TLC-Speichers werden im «SLC-Mode» angesteuert, um zum einen die Datensicherheit für Programmspeicher zu steigern und zum anderen dem langsameren TLC-Speicher als Cache dienen. Ausserdem sorgt die kompakte Bauform für eine gute thermische Kopplung und Unempfindlichkeit gegenüber Umwelteinflüssen wie Schock und Vibration.

Weitere Vorteile sind die Vielfalt an Produkten, die in unterschiedlicher Speichergrösse, mit oder ohne RAM-Cache und verschiedenen Temperaturbereichen bei gleichem Gehäuse zur Verfügung stehen. Für die Evaluierung der SSD auf einem Chip eignet sich gut eine m.2-Steckkarte (siehe Abb. 1), die einfach eingesteckt werden kann. Durch die kompakte Bauweise eignet sich diese Lösung besonders für tragbare Messgeräte und Datenlogger, für Geräte in der Labor- und Medizintechnik sowie durch die geringe Masse für alle Baugruppen, die Vibration und Schock ausgesetzt sind. Da der Speicher aufgelötet und nicht gesteckt ist, ist er sicher gegen Manipulationen durch Auswechseln des Datenträgers.

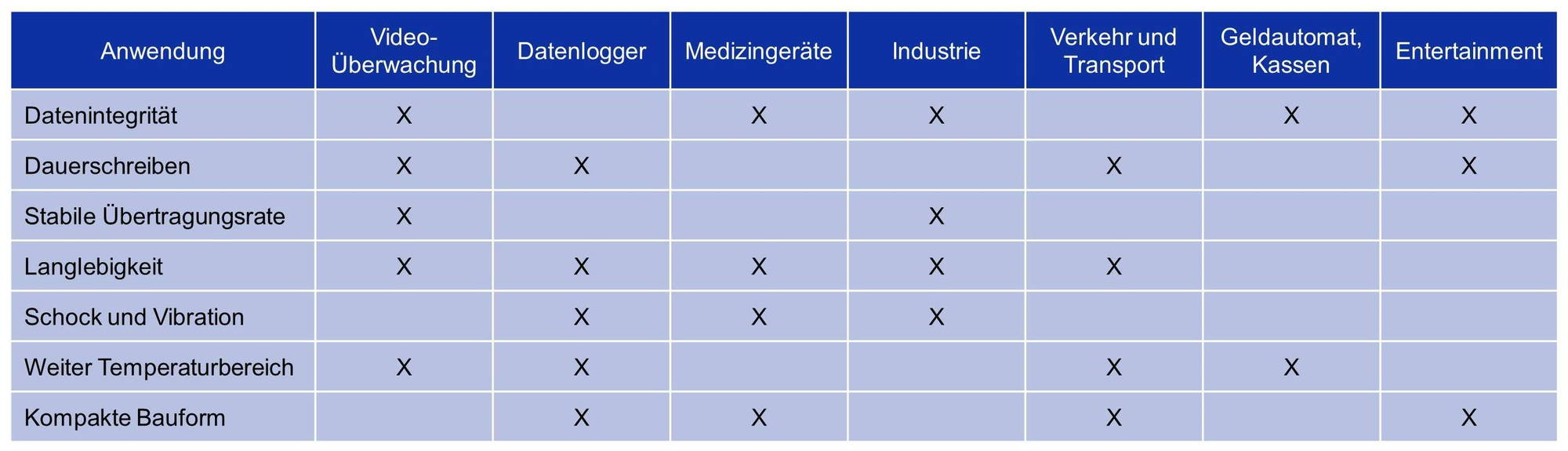

Anforderungen typischer Applikationen

Kapazitäten

Die Flash-Hersteller steigern die Kapazitäten ihrer Chips, indem sie zu höher integrierten Technologien übergehen. Echte SLC-Chips sind kaum noch verfügbar, der Schwerpunkt der Produktion liegt auf TLC. Anwendungen verlangen immer noch die Eigenschaften der SLC-Chips, wie lange Datenhaltung, viele Schreibzyklen und Zuverlässigkeit. TLC-Speicher werden daher in einem niedrigeren «Mode» betrieben, wobei zwar die Kapazität zurückgeht, die Zahl der möglichen Schreibzyklen jedoch ansteigt. Die folgende Tabelle zeigt, welche Kapazitäten mit Chips unterschiedlicher Integrationsdichte zu erzielen sind.

Die «3D NAND»-Technologie platziert mehrere Speicher-Chips (Dies) im Gehäuse übereinander und erzielt so eine hohe Packungsdirchte. Abb. 5 zeigt, welche Netto-Kapazitäten eine SSD auf einem Chip je nach Speicherausbau und dessen Betriebsart erreichen kann.

Ausblick

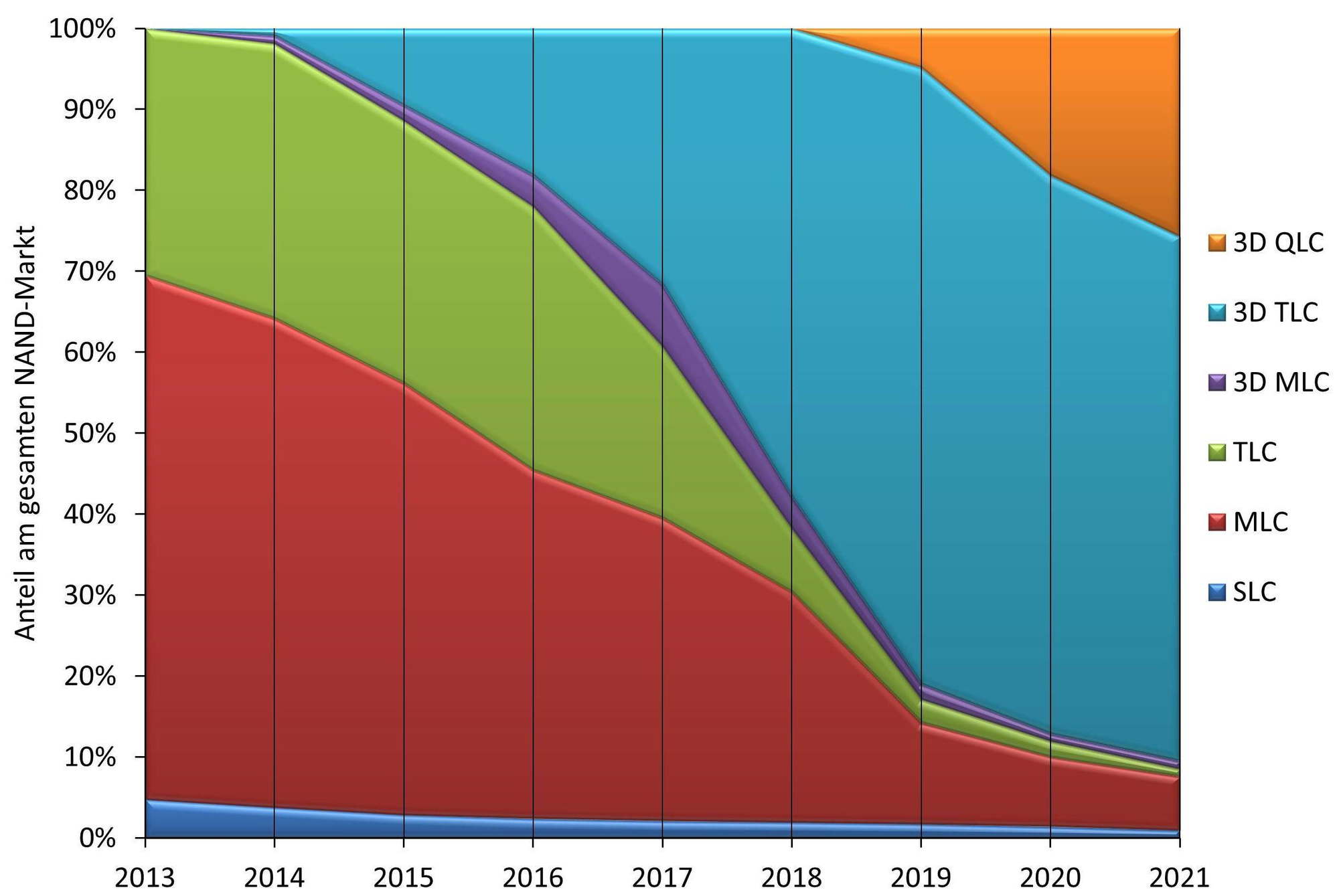

Abb. 6 zeigt die stückzahlbereinigte Verbreitung verschiedener NAND-Flash-Technologien. Während die Versorgung mit NAND-Flash niedriger Integration wie SLC und MLC bereits stark zurückgegangen ist, erscheint am Horizont die neue QLC-Technologie. Die Integrationsdichte in Gigabit pro Chip steigt, und der Preis pro Bit sinkt, so dass die Kosten pro Chip annähernd gleichbleiben werden. Die TLC-Technologie hat durch die Inbetriebnahme neuer Fertigungslinien Fahrt aufgenommen und wird den grössten Teil des Marktes übernehmen. Die Bezeichnung 3D steht in der Grafik für die vertikale Anordnung mehrerer Dies

Anwendungsbeispiel 1:

Digitales Videoaufzeichungssystem

Besonders bei Nutzfahrzeugen werden heute verstärkt Kameras zur Überwachung des Arbeitsbereichs eingesetzt. Sie unterstützen den Fahrer/Bediener mit der Darstellung von Bereichen, die er aus seiner Position heraus nicht einsehen kann, z.B. bei der Rückwärtsfahrt, direkt an der Baggerschaufel oder an der Luke für die Müllgefässe. Zur Dokumentation kann das Kamerasignal direkt in einen digitalen Videorecorder eingespeist werden. Das Speichermedium muss eine konstante Mindestdatenrate ermöglichen, um keine Frames zu verlieren, und eine hohe Anzahl Schreibzyklen bieten, die die Lebensdauer des Fahrzeugs möglichst übertrifft. Konventionelle SD-Karten halten nur ein bis zwei Jahre durch.

Typische Einsatzgebiete sind Bau- und Landmaschinen, Flurförderzeuge, Transportfahrzeuge und Schienenfahrzeuge. Auch die gerade diskutierte Tote-Winkel-Erkennung für LKW beim Rechtsabbiegen fordert Kameras mit Aufzeichnung zur Beweissicherung bei Unfällen.

Anwendungsbeispiel 2:

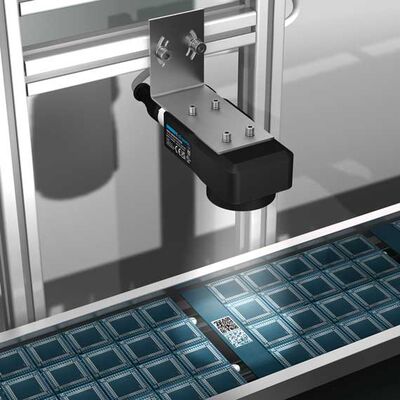

Automatisierte Medikamentenausgabe in der Apotheke

Besonders in grossen Apotheken wie z.B. in Krankenhäusern werden Medikamente in Mengen umgesetzt. Wie kann man die Fehlerrate bei der Ausgabe senken, stets den Lagerbestand kennen und dabei die Verfallsdaten nicht aus den Augen verlieren? Ein automatisiertes System hilft dabei. Eine Schlüsselfunktion übernehmen dabei Kameras, die jede eingelagerte oder abgerufene Medikamentenverpackung scannen und identifizieren. Der Computer führt dabei Buch über alle Transaktionen und kann jederzeit Auskunft über den Lagerbestand geben und Bestellungen disponieren. Die von mehreren Seiten aufgenommenen hochauflösenden Bilder werden in einem Speicher abgelegt, per OCR oder Code dem Datensatz des Medikaments zugeordnet und verbucht. Die dabei eingesetzte SSD muss eine hohe Datentransferrate haben, da die Bilder in rascher Sequenz eingehen, und eine hohe Anzahl Schreibzyklen ermöglichen.

Fazit

Der Integrationsgrad von Flash-basierten Speichermedien wird in der nächsten Zeit weiter steigen. Die Kapazität pro Flash-Chip wird durch die kleineren Halbleiterstrukturen und die QLC-Technologie weiter zunehmen, gleichzeitig wird die Zahl der möglichen P/E-Zyklen aus demselben Grund abnehmen. Für ein zuverlässiges System ist es deshalb umso wichtiger, einen Controller einzusetzen, der den Speicher optimal ansteuert und Funktionen zum Wear Levelling, Fehlerkorrektur und einem stabilen Betrieb mit gleichbleibend hoher Datenrate auch unter widrigen Betriebsumständen sicherstellt.

Die SSD auf einem Chip fasst die wichtigen Funktionsblöcke Host-Controller, Flash-Controller, Flash-Chips und vom Controller-Hersteller in enger Zusammenarbeit mit dem Flash-Hersteller erstellter Firmware monolithisch in einem einzigen IC-Gehäuse zusammen und bietet damit die beste Mischung aus Datenintegrität und Kosten-/Leistungsrelation für alle Embedded-Anwendungen.

Glossar

3D

1. Vertikale Anordnung der Speicherzellen zur Einsparung von Chipfläche bei gleicher Ladungskapazität pro Speicherzelle

2. Stapeln mehrerer Flash-Dies im Gehäuse übereinander, um die Kapazität pro Chip-Gehäuse zu erhöhen

SSD

Solid State Disk, aus Halbleiterbausteinen bestehender Speicher

P/E

Program/Erase-Zyklus. Vor jedem erneuten Beschreiben einer Flash-Zelle muss der gesamte Block, in dem sie sich befindet, gelöscht werden.

SLC

Single Level Cell; eine Speicherzelle enthält zwei Ladungszustände = ein Bit. Siehe auch MLC, TLC und QLC

SLC Mode

Der MLC, TLC oder QLC-Flashspeicher wird betrieben, als könne er nur ein Bit pro Zelle speichern. Vorteile: Grössere P/E, höhere Zuverlässigkeit; Nachteile: geringerer Speicherplatz, höhere Kosten

MLC

Multi Level Cell; eine Speicherzelle enthält vier Ladungszustände = zwei Bits. Siehe auch SLC, TLC und QLC

TLC

Triple Level Cell; eine Speicherzelle enthält acht Ladungszustände = drei Bits. Siehe auch SLC, MLC und QLC

QLC

Quadruple Level Cell; eine Speicherzelle enthält 16 Ladungszustände = vier Bits. Siehe auch SLC, MLC und TLC

Impressum

Autor: Rudolf Sosnowsky, Leiter Technik bei

Hy-Line Computer Components Vertriebs GmbH in Unterhaching

Bildquelle: Hy-Line Computer Components (ausser Abb. 2, 5, 6)

Publiziert von Technik und Wissen (eal)

Informationen

Hy-Line Schweiz

hy-line.ch

Hy-Line Deutschland

hy-line.de

Silicon Motion

siliconmotion.com

UDInfo

udinfo.com.tw

Weitere Artikel

Veröffentlicht am: